【导读】于现代高速数字体系、通讯装备及周详仪器设计中,时钟分配的相位噪声与通道一致性已经成为影响体系机能的要害因素。时序精度上的微小误差可能致使数据收罗过错、通讯误码率上升以致整个体系机能降落。针对于这一挑战,瑞萨电子推出的5PB1102高机能1:2 LVCMOS时钟缓冲器,以其卓着的机能指标为工程师提供了抱负的低噪声、高不变性时钟扇出解决方案。

时序精度的技能冲破

5PB1102时钟缓冲器的焦点上风表现于其卓着的时序保真度上,多项机能指标均到达行业领先程度:

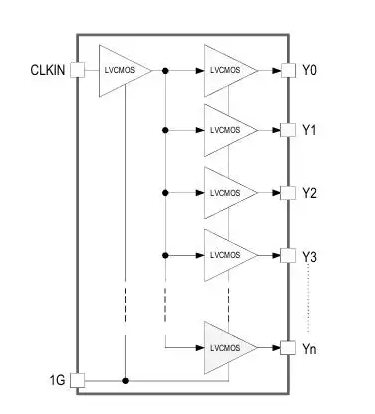

极低附加抖动:该器件典型附加相位抖动值低在50 fs RMS(积分规模12 kHz–20MHz),这一指标远优在同类竞争产物。这类极低的抖动特征确保了参考时钟于分配历程中不会引入显著的相位噪声,为体系提供了纯净的时钟旌旗灯号。

卓着的通道一致性:小在50 ps的输出间偏斜(pin-to-pin skew)保障了多路同步旌旗灯号的严酷对于齐。这一特征对于在并行数据收罗体系、高速ADC/DAC采样时钟以和FPGA全局时钟分配等运用场景至关主要,确保了各个通道间的切确同步。

高速运行能力:最高200 MHz的事情频率使5PB1102可以或许充实满意主流高速接口的时序需求,包括PCIe Gen3/4参考时钟及SerDes参考源等运用。

体系集成与旌旗灯号完备性优化

瑞萨电子于5PB1102的设计中充实思量了现实运用中的体系集成需求:

集成终端电阻:器件内部集成为了50Ω串联终端电阻,这一设计极年夜地简化了PCB结构繁杂度,削减了外部匹配元件的需求。同时,这类集成设计还有有用优化了旌旗灯号完备性,显著按捺了旌旗灯号过冲与振铃征象。

宽电源电压规模:撑持1.8V至3.3V的宽电源电压规模,使该器件可以或许直接适配多种逻辑电平体系,无需分外添加电平转换电路,降低了体系繁杂度及成本。

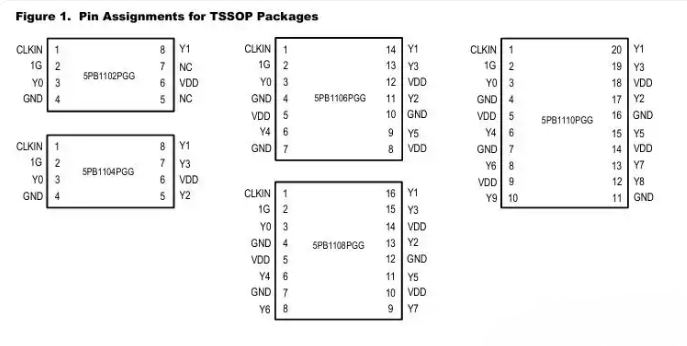

矫捷封装选项:5PB1102提供两种封装选项以满意差别运用场景的需求。8引脚TSSOP封装便在手工焊接与传统SMT工艺;而小型8引脚DFN封装(2妹妹 × 2妹妹)则极年夜地节省了名贵的PCB空间,尤其合适紧凑型模块设计。两种封装均撑持工业级扩大温度规模(–40°C至+105°C),切合汽车电子、工业节制等卑劣情况的苛刻要求。

智能功耗治理与运用场景

5PB1102配备了输出使能(OE)功效,答应体系于待机或者低功耗模式下封闭时钟输出。这一智能特征不仅降低了体系动态功耗,还有有用削减了没必要要的EMI辐射。OE引脚兼容1.8V/3.3V逻辑电平,可直接由MCU或者CPLD节制,提高了体系设计的矫捷性。

该器件的典型运用场景广泛笼罩了多个高要求范畴:

高速ADC/DAC或者RF收发器的参考时钟分配

FPGA或者ASIC的全局时钟树驱动

收集互换芯片的同步以太网(SyncE)时钟扇出

工业主动化中的多轴运动节制同步时钟

汽车雷达与摄像头体系的低抖动时序基准

实践中的设计建议

为了充实阐扬5PB1102的机能上风,于现实运用中应留意如下设计要点:

电源去耦计谋:建议于VDD引脚就近放置100nF陶瓷电容与10μF钽电容组合,以有用按捺高频噪声,确保电源纯净度。

输入旌旗灯号质量要求:为充实阐扬器件的低抖动机能,输入时钟应具有洁净边缘(上升/降落时间tr/tf 2 ns)与充足幅度(≥0.8 VDD)。

PCB布线优化:输出走线应连结等长设计,阔别高频滋扰源,并参考完备地平面,以维持最好的通道一致性。

瑞萨电子5PB1102时钟缓冲器经由过程其卓着的时序保真度、体系集成度及设计矫捷性,为高速数字体系提供了靠得住的时钟分配解决方案。不管是于通讯基础举措措施、工业主动化还有是汽车电子范畴,该器件都能为工程师提供不变、纯净的时钟旌旗灯号,助力体系实现最优机能。跟着数字体系对于时序精度要求的不停提高,这类高机能时钟扇出解决方案的价值将愈发凸显。

-XC-Sports,xc体育